原子层沉积 (ALD) 已经运用了几十年,但是将 ALD 高 K 材料整合为逻辑设备中的栅极电介质以及 DRAM 中的电容器电介质的探索激发了研究界对这项技术的掌握,并扩大了其使用范围。

Veeco/CNT 原子层沉积 (ALD)统用于研究各种高 K 电介质材料,包括 Al2O3、HfO2、Ta2O5、TiO2 和 ZrO2。原子层沉积 (ALD) 技术的灵活性可通过组合薄膜来调整膜性质(即 AlTiO,HfSiO 等),或者通过将氮气掺入这些薄膜中如 AlON、HfON 和 ZrON。原子层沉积 (ALD) 高 K 电介质膜属性包括高电容、低漏电流以及高分解电压,使其适用于电子应用。

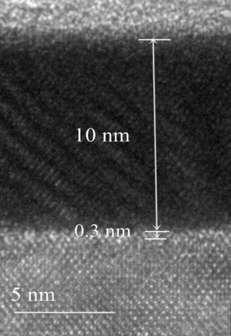

在 Fiji® 上沉积的氮化 HfO2 的 HRTEM。L-T Huang, et al. “Improvement in electrical characteristics of HfO2 gate dielectrics treated by remote NH3 plasma,” Applied Surface Science Volume 266, 1 February 2013, Pages 89-93.

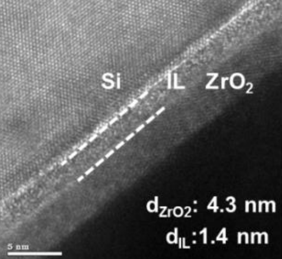

Fiji® 的 HRTEM 在氮化的 Al2O3 缓冲层上沉积 ZrO2。J-J Huang, et al. “Improvement in Electrical Characteristics of Crystalline ZrO2 /Nitrided Al2O3 Gate Stacks Grown by Remote Plasma Atomic Layer Deposition,” ECS J. Solid State Sci. Technol. 2013 volume 2, issue 12, P524-P528

Fiji® 的HRTEM 沉积 ZrO2/Al2O3 堆叠。A. O’Mahoney, et al. “Structural and Electrical Analysis of Thin Interface Control Layers of MgO or Al2O3 Deposited by Atomic Layer Deposition and Incorporated at the high-k/III-V Interface of MO2/InxGa1-xAs (M = Hf|Zr, x = 0|0.53) Gate Stacks,” ECS Transactions, 33 (2) 69-82 (2010).

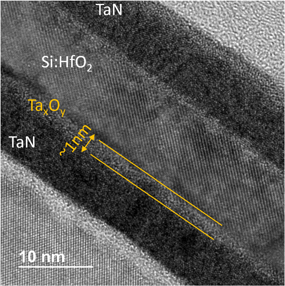

Fiji® 的 HRTEM 沉积 Si:HfO2 膜。P.D. Lomenzo, et al. “TaN interface properties and electric field cycling effects on ferroelectric Si-doped HfO2 thin films,” Journal of Applied Physics 117, 134105 (2015).

主要的逻辑和内存芯片制造商将高 K 原子层沉积 (ALD) 膜集成到其产品中,使得 ALD 技术在制造方面得到了认可,并且在其他器件区域进行了研究,在这些区域中 ALD 膜可以提供性能和成本方面的颠覆性收益。

电极

设备电极材料必须具有适当的属性。低电阻率是主要问题,但其他薄膜性质,包括适当的工作功能和与其他设备材料的化学兼容性至关重要。原子层沉积 (ALD) 可生产一系列纯金属(Pt、Ru、Ni) 以及金属氮化物 (TiN),以及在电子应用中全部用作电极材料的导电氧化物 (RuO2)。

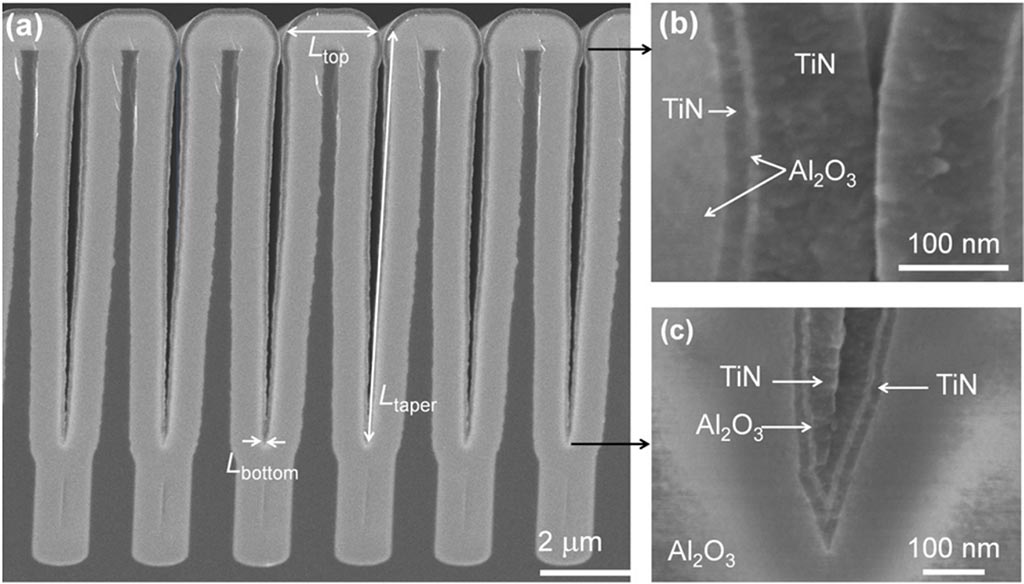

Fiji® 沉积的 TiN-Al2O3-TiN 沟槽电容器的横截面 SEM 图像。M. Burke, et al. “High aspect ratio iridescent three-dimensional metal–insulator–metal capacitors using atomic layer deposition,” J. Vac. Sci. Technol. A 33(1), Jan/Feb 2015.

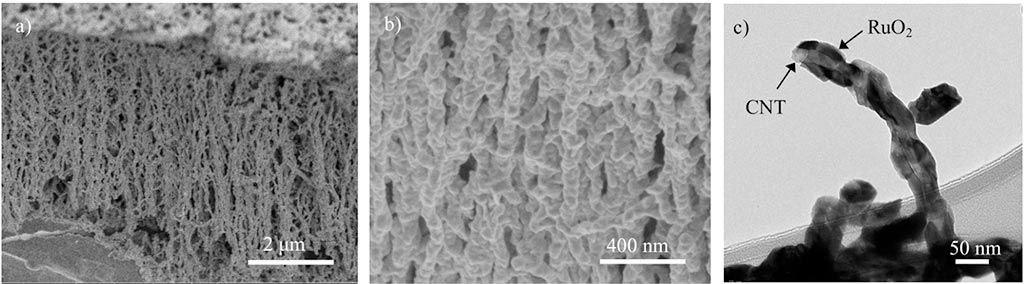

a) 和 b) Fiji® 沉积的 RuO2 包覆的碳纳米管的 SEM 图像以及 c) 单个 RuO2 包覆的碳纳米管的 TEMR. Warren, et al. “ALD Ruthenium oxide-carbon nanotube electrodes for supercapacitor applications,” 2014 IEEE 27th International Conference on Micro Electro Mechanical Systems (MEMS).

阻隔

现代化的集成电路使用纳米级电路、多层接线方案,以将半导体基质上的离散设备互连以生成有用电路,提供配电,并作为片外通信的输入/输出路径。这些互连线通常是沉积在图案化低 K 层间电介质 (ILD) 材料上的细铜线,这些材料支持并定义了连接路径。铜是高迁移率的材料,如果直接沉积在 ILD 上,它将扩散到电介质中,并且随着时间的推移,设备性能将下降。

在铜沉积之前,阻隔膜必须沉积在 ILD 上。阻隔膜越薄、导电性越好,其对互连电阻的总体影响越小。原子层沉积 (ALD) 由于其沉积薄的、共形、无针孔以及具有极低铜扩散特性的高导电膜的能力,尤其适用于阻隔应用。Veeco/Cambridge NanoTech 系统已开发出许多原子层沉积 (ALD) 氮化物工艺。

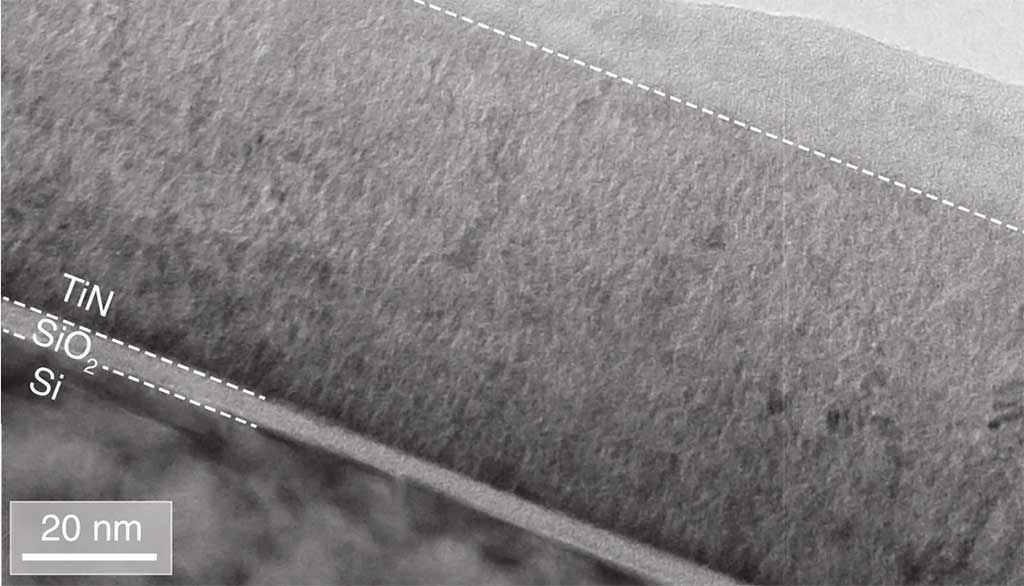

Fiji® 沉积的 TiN 的 TEM 图像。L. Assaud, et al. “Highly-Conformal TiN Thin Films Grown by Thermal and Plasma-Enhanced Atomic Layer Deposition,” ECS Journal of Solid State Science and Technology, 3 (7) P253-P258 (2014).